# Bright et al.

Date of Patent: [45]

Jan. 9, 1990

| [54]    | SECURE O       | COMMUNICATION SYSTEM                                  | 4,612,414 | 9/1986  | Juang   |

|---------|----------------|-------------------------------------------------------|-----------|---------|---------|

| [75]    | Inventors:     | Michael W. Bright, Arlington                          | 4,631,746 | 12/1986 | Berger  |

| [. 0]   | 211 / 01110151 | Heights; Eric F. Ziolko,                              | 4,633,036 | 12/1986 | Hellma  |

|         |                | · ,                                                   | 4,634,808 | 1/1987  | Moerde  |

|         |                | Schaumburg; Alan L. Wilson,                           | 4,642,424 | 2/1987  | McNai   |

|         |                | Hoffman Estates; Michelle M. Bray,                    | 4,654,480 | 3/1987  | Weiss   |

|         |                | Schaumburg; Harry A. Hennen,                          | 4,667,327 | 5/1987  | Bright  |

|         |                | Woodstock; David L. Weiss, Roselle,                   | 4,680,791 | 7/1987  | Kato e  |

|         |                | all of Ill.                                           | 4,680,797 | 7/1987  | Benke   |

| [73]    | Assignee:      | Motorola, Inc., Schaumburg, Ill.                      | 4,688,257 | 8/1987  | Erickso |

|         | _              | , ,                                                   | 4,697,264 | 9/1987  | Galens  |

| [21]    | Appl. No.:     | •                                                     | 4,697,277 | 2/1987  | Van Ra  |

| [22]    | Filed:         | Sep. 30, 1986                                         | 4,719,643 | 1/1988  | Beeman  |

| [51]    | Int. Cl.4      | H04K 1/00                                             | 4,723,246 | 2/1988  | Weldon  |

| Ī52Ī    | U.S. Cl        | <b>380/28;</b> 380/21;                                | 4,742,546 | 5/1988  | Nishim  |

| t1      | _ ,            | 380/43; 380/46; 380/48                                | 4,744,080 | 5/1988  | Brenna  |

| [58]    | Field of Sea   | rch 178/22.10, 22.13, 22.17;                          | 4,752,953 | 6/1988  | Paik et |

| [-0]    |                | 9/1.5 S; 380/28, 21, 46, 48, 29, 30, 43; 364/200, 900 |           | EIGN P  |         |

| F. C. 7 |                | D. C. Cit. I                                          | 0178608A2 | 4/1986  | Europe  |

#### [56] References Cited

# U.S. PATENT DOCUMENTS

| 2,777,897 | 1/1957  | Gretener et al 380/8        |

|-----------|---------|-----------------------------|

| 3,586,776 | 6/1971  | Salava 178/69.5 R           |

| 3,610,828 | 10/1971 | Billerica et al 380/48      |

| 3,852,534 | 12/1974 | Tilk 370/107                |

| 3,906,445 | 9/1975  | Beckmann et al 340/146.1 BA |

| 4,020,285 | 4/1977  | Branscome et al 380/21      |

| 4,052,565 | 10/1977 | Baxter et al 380/28         |

| 4,086,435 | 4/1978  | Graupe et al 380/49         |

| 4,126,761 | 11/1978 | Graupe et al 380/28         |

| 4,149,035 | 4/1979  | Frutiger 380/36             |

| 4,158,748 | 6/1979  | En 178/69.1                 |

| 4,167,700 | 10/1979 | Coe et al 325/32            |

| 4,171,513 | 10/1979 | Otey et al 380/43           |

| 4,182,933 | 1/1980  | Rosenblum 380/21            |

| 4,243,941 | 1/1981  | Zdunek 329/50               |

| 4,266,243 | 5/1981  | Shutterly 179/1.5 S         |

| 4,268,720 | 5/1981  | Olberg et al 380/36         |

| 4,271,520 | 6/1981  | Coombes et al 371/42        |

| 4,302,628 | 11/1981 | Akrich et al 380/43         |

| 4,354,265 | 10/1982 | Nyberg et al 370/111        |

| 4,394,760 | 7/1983  | Kammerlander 370/111        |

| 4,411,017 | 10/1983 | Talbot 455/26               |

| 4,434,323 | 2/1984  | Levine et al 179/1.5 S      |

| 4,484,027 | 11/1984 | Lee et al 380/21            |

| 4,516,241 | 5/1985  | Farah et al 370/110.1       |

| 4,567,591 | 1/1986  | Gray et al 370/109          |

| 4,608,456 | 8/1986  | Paik et al 179/1.5 S        |

| 4,611,342 | 9/1986  | Miller et al                |

|           |         |                             |

| 4,612,414 | 9/1986  | Juang 380/41             |

|-----------|---------|--------------------------|

| 4,631,746 | 12/1986 | Bergeron et al 381/35    |

| 4,633,036 | 12/1986 | Hellman et al 380/30     |

| 4,634,808 | 1/1987  | Moerder 380/46           |

| 4,642,424 | 2/1987  | McNair 380/48            |

| 4,654,480 | 3/1987  | Weiss 380/48             |

| 4,667,327 | 5/1987  | Bright et al 371/47      |

| 4,680,791 | 7/1987  | Kato et al 380/8         |

| 4,680,797 | 7/1987  | Benke 381/41             |

| 4,688,257 | 8/1987  | Erickson 380/48          |

| 4,697,264 | 9/1987  | Galensky et al 370/111   |

| 4,697,277 | 2/1987  | Van Rassel 375/116       |

| 4,719,643 | 1/1988  | Beeman 375/115           |

| 4,723,246 | 2/1988  | Weldon, Jr 371/42        |

| 4,742,546 | 5/1988  | Nishimura et al 380/28 X |

| 4,744,080 | 5/1988  | Brennand et al 380/21    |

| 4,752,953 | 6/1988  | Paik et al 380/9         |

|           |         |                          |

#### **IT DOCUMENTS**

4/1986 European Pat. Off. .

# OTHER PUBLICATIONS

E. D. Rainville, Elementary Diff. Eq.s; (MacMillan,

1981; pp. 95-96).

J. L. Fike et al., Understanding Telephone Electronics; (Sams & Co., Indianapolis; 1983; pp. 6-24, 6-25, 6-28 to

Friend et al., Understanding Data Comm.; (Sams & Co., Indianapolis; 1984; pp. 2-20 to 2-28).

"Privacy and Authentication: An Introduction to Cryptography" by Whitfield Diffie, and Martin E. Hellman, Proceedings of the IEEE, vol. 67, No. 3, Mar. 1979.

Primary Examiner—Stephen C. Buczinski Assistant Examiner—Bernarr Earl Gregory Attorney, Agent, or Firm-Thomas G. Berry; Steven G. Parmelee

# ABSTRACT

Disclosed is a synchronous secure communication system wherein an information signal is encrypted in an encryption means. The encrypted signal is compressed to allow the insertion of a synchronization signal, and the combined signals are transmitted. At the receiver, the synchronization signal is extracted and used to synchronize the receiver to the incoming data stream thereby improving receiver sensitivity and range.

#### 53 Claims, 12 Drawing Sheets

Jan. 9, 1990

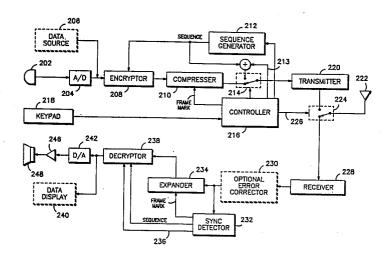

FIG.4 208

FIG. 12 238

| S. Paten                                                                       |          | Jan. 9, 1990  |           |        | Sheet 7 of 12 |         |        |        | 4,893,339     |                                                                                                    |

|--------------------------------------------------------------------------------|----------|---------------|-----------|--------|---------------|---------|--------|--------|---------------|----------------------------------------------------------------------------------------------------|

|                                                                                |          |               |           |        |               |         |        |        |               |                                                                                                    |

|                                                                                | RAM<br>O | ADDRES<br>1   | SSES<br>2 | 3      | 4             | 5       | 6      | 7      | 8             | OUTPUT                                                                                             |

| CLOCK CYCLES                                                                   | WR       | WR            | WR        | WR     | WR            | WR<br>W | R<br>W | R<br>W | В             | SIGNAL<br>SIGNAL<br>SIGNAL<br>SIGNAL<br>SIGNAL<br>SIGNAL<br>SIGNAL<br>SIGNAL                       |

| 012345678901112345678901123456789011234456789011234456789011234456789011234442 | R<br>W   | R<br>W<br>W   | R<br>W    | R<br>W | R<br>W        | R<br>W  | R      | w<br>R | R<br>W        | SIGNAL<br>0<br>1<br>2<br>3<br>4<br>6<br>7<br>8<br>9<br>10<br>12<br>13<br>14<br>15                  |

| 17<br>18<br>19<br>20<br>21                                                     | R<br>W   | R             | R         | R      |               |         | W      | w      | R<br>W        | 9<br>10<br>12<br>13<br>14                                                                          |

| 22<br>23<br>24<br>25<br>26                                                     |          | W             | W<br>W    | w      | R<br>W        | R       | R      | R      | R             | 15<br>16<br>18<br>19<br>20                                                                         |

| 27<br>28<br>29<br>30<br>31                                                     | R        | R             | R         | R      | R             | W       | w      | w<br>w | w             | 21<br>22<br>24<br>25<br>26                                                                         |

| 32<br>33<br>34<br>35                                                           | W<br>R   | w             | w         | W      |               | R       | R      | ·R     | R             | 27<br>28<br>30<br>31                                                                               |

| 37<br>38<br>39<br>40<br>41                                                     | K        | R             | R         | "<br>R | W<br>R        | W<br>R  | W<br>R | w      | W             | 16<br>18<br>19<br>20<br>22<br>24<br>25<br>26<br>27<br>28<br>30<br>31<br>33<br>34<br>37<br>38<br>39 |

| 43<br>44<br>45<br>46<br>47<br>48                                               | W<br>R   | <b>W</b><br>R | W<br>R    | W<br>R | W<br>W<br>R   |         | K      | R      | R             | 40<br>42<br>43<br>44<br>45<br>46                                                                   |

| 43<br>44<br>45<br>46<br>47<br>49<br>55<br>55<br>55<br>55                       | W<br>WR  | WR            |           |        | R             | W<br>R  | W<br>R | W<br>R | <b>W</b><br>R | 48<br>49<br>50<br>51<br>52<br>SIGNAL<br>SIGNAL                                                     |

FIG.7

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |             | <b>,</b>    |        |             |             |             |             | ,                                                                        | ,                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------------|-------------|--------|-------------|-------------|-------------|-------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | RAM<br>0 | ADDRES      | SSES<br>2   | 3      | 4           | 5           | 6           | 7           | 8                                                                        | OUTPUT                                                                                    |

| CLOCK CYCLES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | WR       | WR          | WR          | WR     | WR          | WR<br>R     | W<br>R      | w           |                                                                          | 0<br>1<br>2<br>3<br>4<br>PREDICT<br>5<br>6<br>7<br>8<br>9<br>PREDICT                      |

| SEQUENCE CYCLES 34 2 6 2 8 8 9 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | W<br>R   | W<br>R<br>R | W<br>R      | W<br>R | W<br>R      | W<br>R      | w           | W<br>R<br>W | W<br>R                                                                   | 7<br>8<br>9<br>PREDICT<br>10<br>11<br>12<br>13<br>14<br>PREDICT                           |

| 17<br>18<br>19<br>20<br>21<br>22<br>23<br>24<br>25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W ·      | W<br>R      | W<br>R<br>R | W<br>R | w           | w           | R<br>R<br>W | R           | W<br>R                                                                   | 15<br>16<br>17<br>18<br>19                                                                |

| 26<br>27<br>28<br>29<br>30<br>31<br>32                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | W<br>R   | W           | w           | w      | R<br>W      | R<br>W      | R           | R<br>R      | W<br>R                                                                   | PREDICT<br>20<br>21<br>22<br>23<br>24<br>PREDICT<br>25<br>26<br>27<br>28<br>29<br>PREDICT |

| 35<br>35<br>36<br>37<br>38<br>39<br>40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | W        | R R<br>W W  | R<br>R<br>W | R<br>W | R           | R           | W<br>R      | W           | PREDICT<br>30<br>31<br>32<br>33<br>34<br>PREDICT<br>35<br>36<br>37<br>38 |                                                                                           |

| z 45                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R<br>W   | R<br>W      | R<br>W      | R<br>W | R<br>R<br>W | r<br>R<br>W | w           | W           | R<br>R<br>W                                                              | 35<br>36<br>37<br>38<br>39<br>PREDICT<br>40<br>41                                         |

| SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHRONIZATIO<br>SYNCHR | R<br>WR  | WR          |             | E      | · / /       | . 1         | R<br>W      | R<br>W      | R<br>W                                                                   | 98<br>39<br>PREDICT<br>40<br>41<br>42<br>43<br>44<br>PREDICT<br>45<br>46                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |          |             |             | T.     | 10          | /           |             |             |                                                                          |                                                                                           |

4,893,339

Sheet 11 of 12

**U.S. Patent** Jan. 9, 1990

### SECURE COMMUNICATION SYSTEM

#### TECHNICAL FIELD

This invention relates generally to two-way communication systems and more particularly to secure twoway communication systems and is particularly directed toward providing a two-way secure voice communication system.

# **BACKGROUND ART**

Secure communications systems are known. The goal of such systems is to render a message unintelligible so as to prevent unauthorized reception. Typically, a message, such as a voice message, is digitized and processed 15 through an encryption device to produce a signal that is random or pseudo-random in nature, thus appearing noise-like to the unauthorized receiver. The particular encryption algorithm used by the encryption device may be a proprietary algorithm, or may be based on a 20 standard such as the Data Encryption Standard (DES) promulgated by the National Bureau of Standards (NBS), of the United States Government.

Generally, it is known to operate a selected encryption device in the cipher feedback (CFB) mode, 25 wherein the cipher text output signal is added (modulo two) with the plain text input signal; the result being feedback into the encryption device. As used herein, cipher text means the encrypted unintelligible signal transmitted from, or received by, an encryption device 30 operating within a secure communication system. Further, as used herein, plain text means the unencrypted (or "clear") signal transmitted from, or received by, an encryption device operating within a secure communication system. Those skilled in the art will appreciate 35 receiver sensitivity and range. that the wide utilization of the CFB mode of operation was due chiefly to the self-synchronizing signal (as related to encryption synchronization) that is produced. In fact, the NBS has suggested that secure communication equipment suppliers employing the D.E.S. design 40 their systems to operate in the CFB mode.

However, a secure communication system having transceiving devices that operate in the CFB mode suffers a serious detriment in that the transceiving devices have a reduced operational range. The range re- 45 duction is caused by error multiplication in the receiver, which manifests itself as degraded receiver sensitivity. The error multiplication is fundamental to the CFB concept since an erroneously received bit is applied to the encryption algorithm input until the error finally 50 "clears" or is shifted out of the algorithm input register. Thus, for D.E.S. with an input register of 64 bits, a single erroneously received bit produces sixty-four errors in the plain text output stream. Receiver sensitivity reduction of 4-6 dB is typical, and, depending on the 55 transmitter power, may result in a range reduction measured in miles. Therefore, a need exists for a secure communication system to overcome the range reduction problem of the prior art.

#### SUMMARY OF THE INVENTION

Accordingly, it is an object of the present invention to provide an improved secure communication system.

It is a further object of the present invention to provide a synchronous secure communication system hav- 65 detector of FIG. 2; ing extended range.

It is another object of the present invention to provide a synchronous transceiving device capable of oper-

ating in the secure communication system of the present invention.

It is yet a further object of the present invention to provide a synchronous receive-only device capable of operating in the secure communication system of the present invention.

It is still another object of the present invention to provide a means for especially adapting prior CFB devices thereby enabling them operating within the extended range secure communication system of the present invention.

It is yet another object of the present invention to provide a method for compressing a digital signal to insert a synchronization signal.

It is still a further object of the present invention to provide an improved synchronization detector for use in a secure communication system.

It is yet a further object of the present invention to provide a method for expanding a compressed digital signal with bit prediction.

It is the final object of the present invention to provide a synchronous secure communication system having extended range.

It is the ultimate object of the present invention to provide an improved secure communication system.

Briefly, according to the invention, a synchronous secure communication system is provided wherein an information signal is encrypted in an encryption means. The encrypted signal is compressed to allow the insertion of a synchronization signal, and the combined signals are transmitted. At the receiver, the synchronization signal is extracted and used to synchronize the receiver to the incoming data stream thereby improving

# BRIEF DESCRIPTION OF THE DRAWINGS

The features of the present invention which are believed to be novel are set forth with particularity in the appended claims. The invention, together with further objects and advantages thereof, may be understood by reference to the following description, taken in conjunction with the accompanying drawings, and the several figures of which like reference numerals identify like elements, and in which:

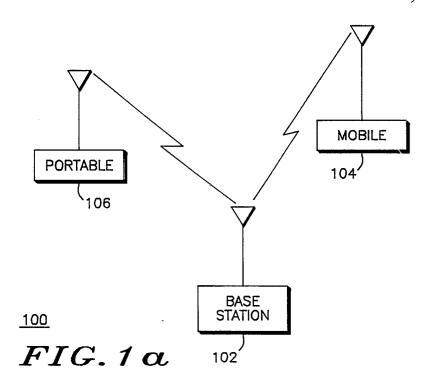

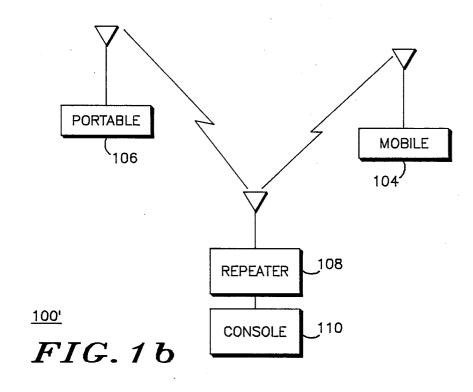

FIGS. 1a-b are a block diagrams of the secure communication system of the present invention;

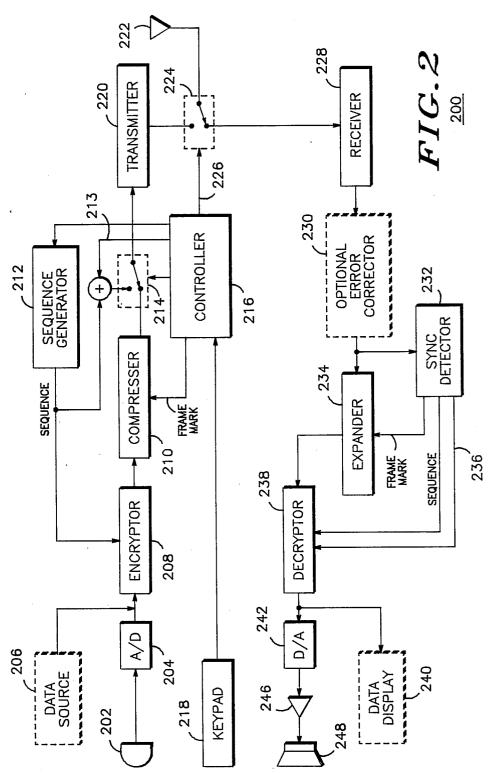

FIG. 2 is a block diagram of a transceiving device capable of operating in the system of FIG. 1;

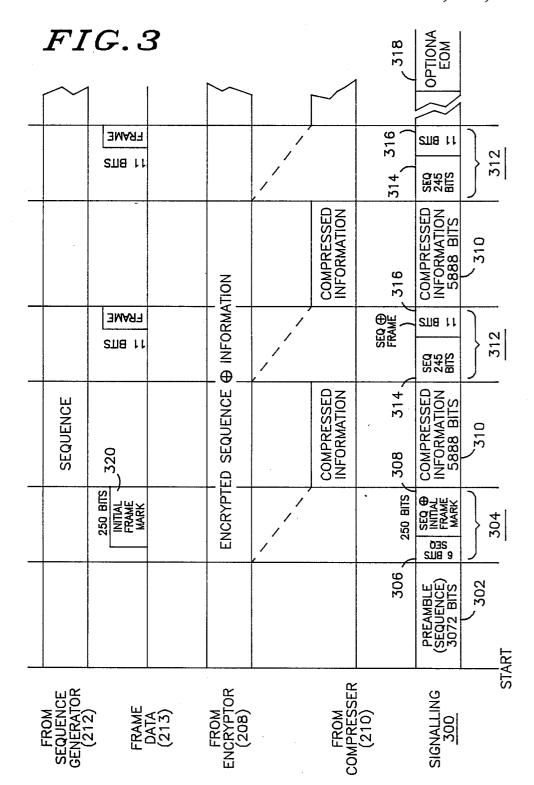

FIG. 3 is an illustration of the preferred signalling format of the present invention;

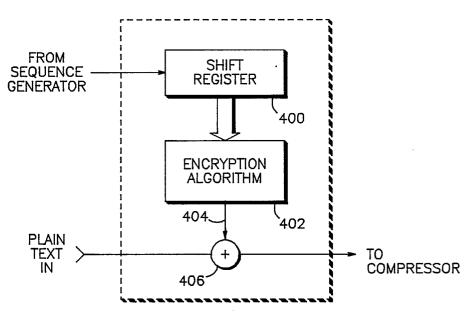

FIG. 4 is a block diagram illustrating the preferred mode of operation of the encryptor of FIG. 2;

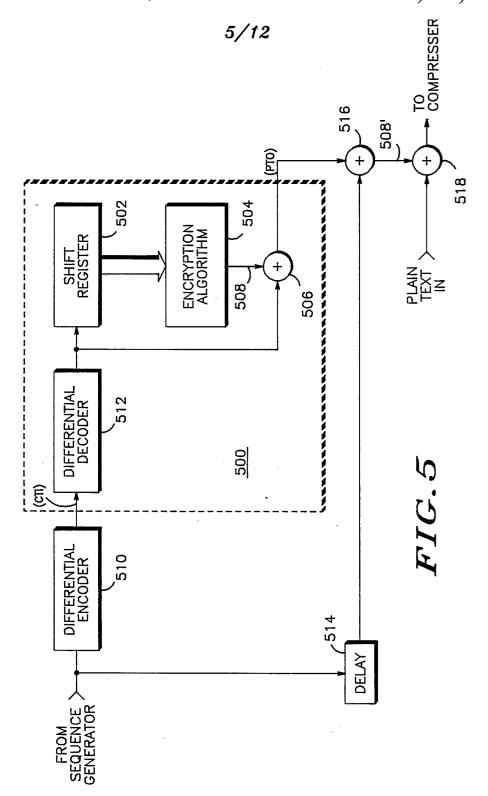

FIG. 5 is a block diagram illustrating how a CFB encryption device may be especially adapted to operate in the system of FIG. 1;

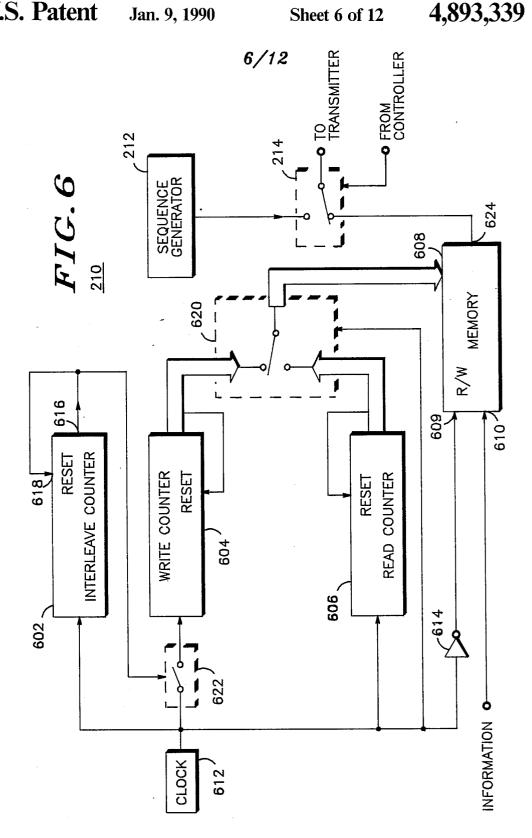

FIG. 6 is a block diagram of the compressor of FIG. 2:

FIG. 7 is a chart illustrating the operation of the compressor of FIG. 6;

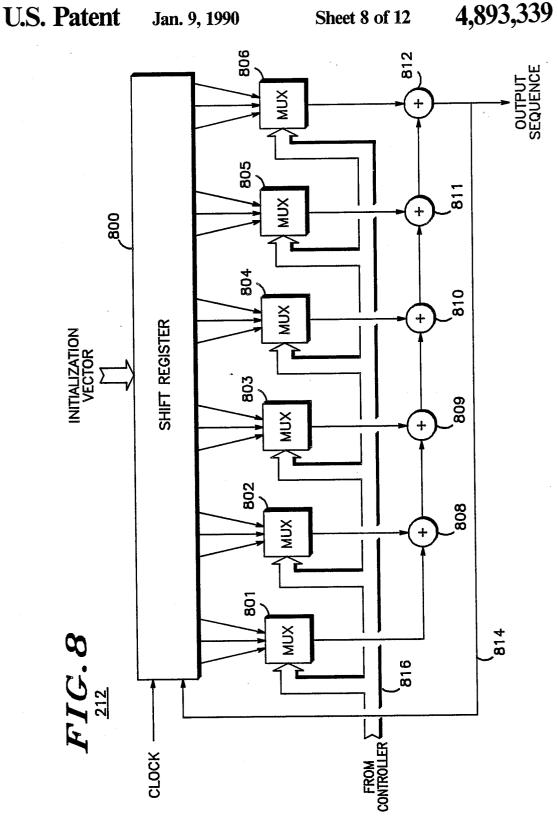

FIG. 8 is a block diagram of the sequence generator of FIG. 2;

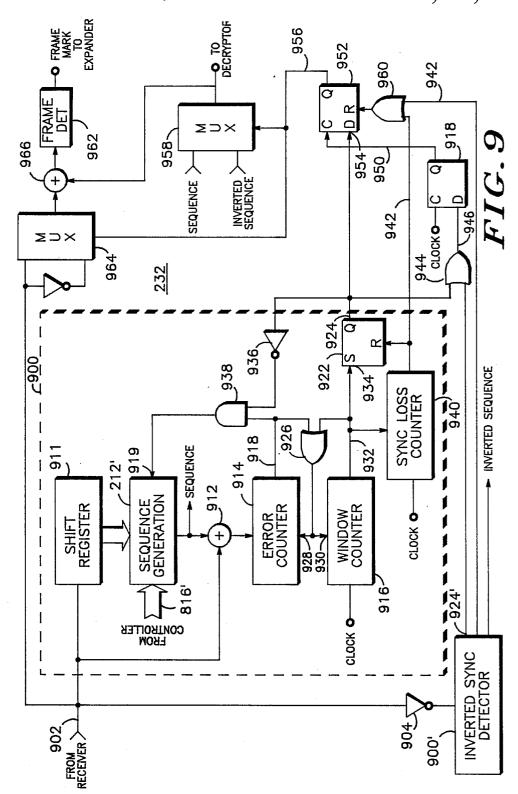

FIG. 9 is a block diagram of the synchronization

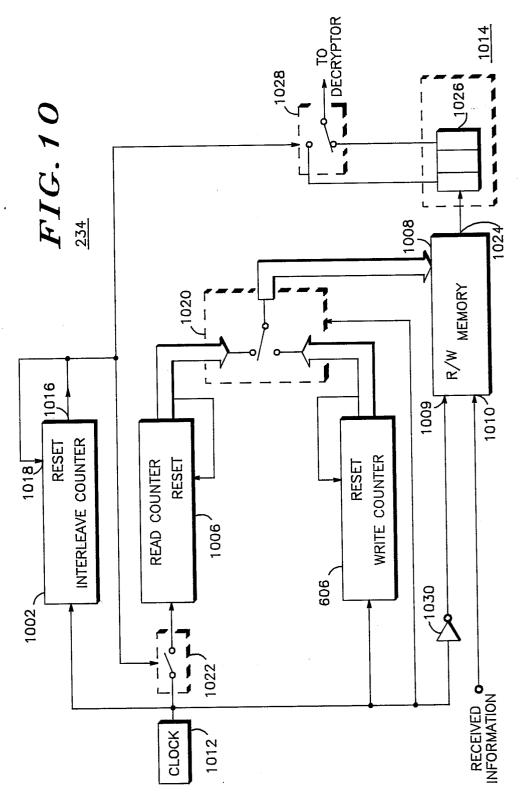

FIG. 10 is a block diagram of the expander of FIG. 2; FIG. 11 is a chart illustrating the operation of the expander of FIG. 10;

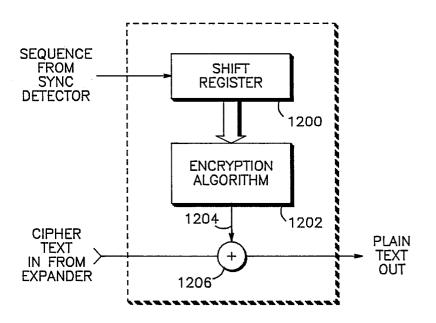

FIG. 12 is a block diagram illustrating the preferred mode of operation of the decryptor of FIG. 2;

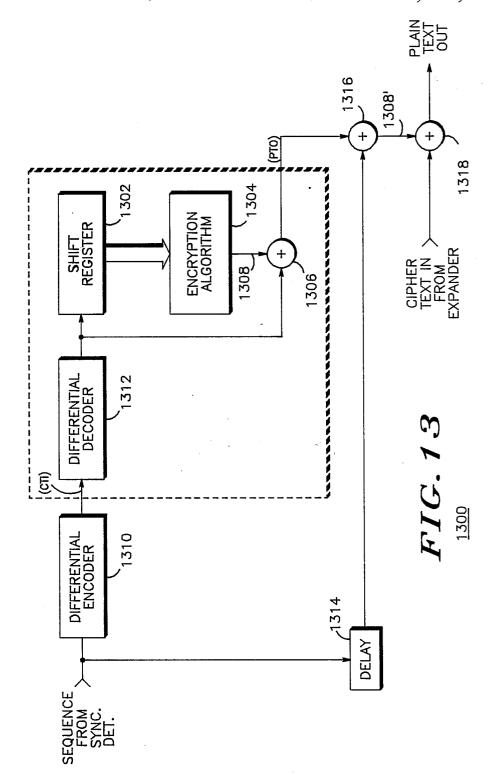

FIG. 13 is a block diagram illustrating how a CFB decryption device may be especially adapted to operate to operate in the system of FIG. 1.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

Referring now to the drawings and in particular to FIG. 1a, there is shown a block diagram of the secure 10 signal to the operator. communication system 100 of the present invention. Basically, the secure communication system 100 is comprised of at least one base station 102, and a plurality of remote units 104 and 106. In FIG. 1b, a console 110 Preferably, the repeater 108 operates to repeat an encrypted message without decrypting it locally. In this way, end-to-end security of the message is maintained. Moreover, "transparent" repeaters that do not locally decrypt the message do not require the "encryption 20 key", and thus, provide a system advantage in that a system operator need not commute to each repeater site to periodically change the encryption key to maintain system security. The remote units communicating on this system may include mobile units 104, or portable 25 units 106. Typically, mobile units are understood to be transceivers designed to operate in a vehicle. A portable unit is typically understood to be a transceiving or receive-only device designed primarily to be carried on or ally permanent or semi-permanent installations in buildings or other such fixed locations. As used herein, any of these devices that are capable of encrypting and decrypting an information signal to communicate within the secure communication system 100 are collec- 35 tively referred to as transceiving devices.

Referring now to FIG. 2, a transceiving device 200 capable of operating in the secure communication system 100 of FIG. 1 is shown. To transmit a message, an information signal, such as a voice signal, is provided by 40 the microphone 202 to the analog-to-digital (A/D) converter 204. The A/D 204 may be any suitable device which provides a digital representation of the voice signal, and preferably is a Continuously Variable Slope appreciate that human speech contains a large amount of redundant information. Speech production may be modeled as an excitation signal (i.e., air from the lungs) driving a filter (the vocal tract), which possesses a certain resonant structure. The spoken sound changes with 50 time since the filter varies with time. The excitation is noise-like for unvoiced sounds (i.e., consonants) and appears as a periodic excitation for voiced sounds (for example vowels). The continuous noise-like consonants, duces a voice signal having a highly redundant information content.

Referring still to FIG. 2, the speech signal is digitized in the A/D 204, which preserves the redundancy in the speech signal. It is especially convenient if the tech- 60 nique used to digitize an inherently redundant voice signal produces redundant digital patterns. Such techniques are known in the art and preferably a CVSD device is used since they are known to produce a digital ros". Alternately, a data source 206 may provide the information signal, which may be any data signal (such as computer data) provided that the data signal con-

tains, or may be adapted to contain, redundant information. One method known in the art for adapting a data signal to contain redundant information is interpolation sampling wherein a data bit is held in a sample and hold device and its logical state clocked out for a predetermined number of times. In this way, each data bit may be replicated within the data stream thereby providing redundancy. At the receiver, the redundant bits are simply discarded prior to presenting the information

The digital information (plain text) signal is applied to an encryptor 208, which encrypts the information signal producing a random or pseudo-random encrypted signal that preferably resembles a noise signal. Preferably, communicates with the remote units via a repeater 108. 15 the encryptor 208 is coupled to the sequence generator 212 such that it operates in the Counter Addressing (CA), or linear recursion, mode as will be hereinafter fully described. Those skilled in the art will appreciate that any digital encryption device may be used as the encryptor 208, including CFB devices so long as they are especially adapted for use with the present invention as will also hereinafter be fully described. The encrypted (cipher text) signal is provided to the compressor 210, which discards selected bits or small groups of bits of the encrypted signal and compresses the remaining bits to make room for a synchronization signal supplied by a sequence generator 212. Preferably, the sequence generator 212 is capable of providing a plurality of synchronization signals, each of which is random or about the person. Base stations, and repeaters are usu- 30 pseudo-random in nature since they are interleaved with the encrypted signal. The plurality of synchronization signals may be used as group identification (ID codes) to divide, for example, Police and Fire departments, or other such tactical groups operating on the same system. Moreover, a "dummy" synchronization signal may be used by the secure communication system of the present invention to continuously transmit information, such as an electronically stored copy of a textbook or encyclopedia, so that there is continuous "traffic" on the system. In this way, the unauthorized receiver will not be able to detect the information traffic increase that typically occurs during the handling of an emergency. Of course, to continuously transmit information and still receive a message, the antenna switch Delta-Modulator (CVSD). Those skilled in the art can 45 224 must be replaced by a duplexer as known in the art. One of the plurality of synchronization sequences may be selected by the controller 216 to be combined with any particular message. At the conclusion of the information message, the dummy sequence may be reselected to maintain continuous transmission. Alternately, a predetermined digital word may be used as the synchronization signal, however, the security of the communication system may be comprised since the unauthorized receiver may easily determine which porcombined with the periodic excitation of vowels, pro- 55 tion of the signal is encrypted information and which is merely synchronization information.

The synchronization signal is interleaved with the compressed encrypted signal via the switch 214. The switch 214 is controlled by a controller 216, which may be a microprocessor or suitable equivalent. The controller 214 is programmed to periodically and systematically operate the switch 214 such that the synchronization signal is properly inserted into the space provided by the compressor 210. In addition, the controller adds waveform having several consecutive "ones" and "ze- 65 frame data information 213 to the sequence so that the compressor and expander can be properly synchronized. Preferably, the controller 216 is programmed with standard operating (default) parameters which

determine, for example, the selection of the synchronization sequence and the interleave rate of the synchronization signal into the compressed encrypted signal. These default parameters may be optionally over-riden by user specified parameters provided by a keypad 218 or other such data entry device. Additionally, the keypad 218 may be used to input the encryption key that will be used by the encryptor 210 and the decryptor 238. Alternately, the positions of the encryptor 208 and the time compressor 210 may be interchanged. In this 10 alternate embodiment, the digital information signal is first compressed and then encrypted prior to combination with the synchronization signal. However, the preferred embodiment is to first encrypt and then compress since this allows flexible re-formatting of the syn- 15 chronization signal interleave rate (such as by the operator) without having to de-crypt the signal and re-compress to provide a different synchronization sequence or format.

Still referring to FIG. 2, the combined digital signal is 20 routed to a transmitter 220. The transmitter 220 may be any suitable transmitter, and the description of any particular transmitter is not prerequisite to the full understanding the present invention. To transmit the message, the transmitter is temporarily coupled to the an- 25 tenna 222 via the antenna switch 224. The antenna switch 224 is controlled by the controller 216 via the connection 226. Typically, the controller 216 operates the antenna switch 224 in response to an operator provided signal such as a push-to-talk (PTT) signal as is 30 well known in the art. Normally, the transceiving device 200 operates in the receive mode with the antenna 222 coupled to a receiver 228 via the antenna switch 224. As previously mentioned in connection with the transmitter 220, any suitable receiver may be used in the 35 transceiving device 200 of the present invention and the description of any particular receiver is not prerequisite to the full understanding the present invention. The receiver 228 provides the received signal to an optional error corrector 230. Those skilled in the art will appre- 40 ciate that the received digital signal may have erroneous bits do to signal fading or other such adverse signal conditions. Accordingly, some receiver designers prefer to employ error correction at the receiver to improve the receiver's performance. Proper reception of 45 the synchronization signal is particularly important since no information will be delivered to an operator until the receiver is "in sync". Thus, the present invention contemplates the optional use of an error corrector 230. If error correction is desired, the preferred embodi- 50 ment of its incorporation is fully disclosed in U.S. Pat. No. 4,747,105 which is thereto as if fully set forth herein. Also, a preferred method of error correcting a pseudo-random synchronization sequence is described in U.S. Pat. No. 4,667,327.

The received sequence is next applied to a synchronization detector 232 and an expander 234. The synchronization detector 232 locates the synchronization signal in the received signal and provides a synchronization detect signal 236 if synchronization is achieved. Additionally, the synchronization detector provides framing information to the expander 234 so that the encrypted signal may be expanded back to its original form. As previously mentioned, the compressor periodically removed a bit or small group of bits so that the signal 65 could be compressed. For proper reception, the synchronization signal must be extracted and the removed bits replaced in their proper position. This is accom-

6

plished in the expander 234 by predicting the removed bit from information gathered from the surrounding bits, which contain information of the logical state of the removed bit due to the redundant nature of the information signal. The expanded signal is received by a decryption device 238, which may be any suitable device capable of recovering the information signal from whatever encryption device 208 is used. Of course, if the encryptor 208 and the compressor 210 were reversed, the expander 234 and the decryptor 238 would also be reversed. The output of the decryptor 238 is the original information signal (plain text). If the information was data, the information may be displayed to the operator via any suitable display device 240. If the information signal was a voice signal, the digitized representation must be first converted back to an analog signal in a digital-to-analog (D/A) convertor 242. The now analog signal may be amplified in an audio amplifier 246 and provided to the operator via a speaker 248. In this way, messages may be transmitted and received using the transceiving device 200 of the present invention.

From the foregoing, it will be readily apparent to those of ordinary skill in the art that a receive-only device may be readily implemented using only the receive portion of FIG. 2, taken in conjunction with the detailed description above. Receive-only devices capable of operating in the secure communication system 100 of the present invention include, but are not limited to, data display pagers or terminals (using the data display 240), tone or tone-and-voice pagers (using the D/A 242, the audio amplifier 246 and the speaker 248) and, without the compress/expand and encryption, as a data detector in base equipment for data regeneration. The receive-only devices may be arranged in groups by judicious selection of operable synchronization sequences as described hereinabove in connection with the transceiving devices.

Referring now to FIG. 3, the preferred signalling format 300 is shown. Initially, a suitable preamble portion 302 is transmitted so that a receiver may acquire bit and sequence synchronization. Bit synchronization may be done by any of the many techniques known in the art. The length of the preamble is not critical, however, 3072 bits is preferred. The preamble is a portion of the synchronization sequence. Next, the initial frame mark data 308 for the expander 208 is sent in interval 304. Preferably this is composed of a continuation of the synchronization sequence 306 (6 bits), and the continued synchronization sequence exclusive ORed with a 250 bit sequence generated by an eight stage maximal length linear feedback shift register sequence generator (308). The use of the 250 bit sequence assures an accurate initial frame mark at the receiver. The 256 bit 55 length of interval 304 is conveniently chosen to be compatible with succeeding synchronization and frame mark intervals (312). This length may be user selected as previously mentioned. Following the synchronization block 304, a portion of the information signal (now encrypted and compressed) is transmitted in block 310. Preferably, 5888 encrypted information bits are transmitted in the information portion 310, which together with the synchronization block 304, form a frame having a length of 6144 bits. Optionally, as previously mentioned, both the information portion and the frame length may be user selected. After the information block 310, and interleaved throughout the remainder of the message, is the synchronization and frame mark

block 312. Preferably 312 is composed of a portion of the synchronization sequence 314 (245 bits), and the continued synchronization sequence exclusive ORed with an eleven bit frame marker pattern 316. Block 312 allows synchronization and frame marking to occur in 5 the event that blocks 302 and 304 are not received. It also allows the continued detection of the synchronization to be verified. Preferably, the format 300 concludes with an end-of-message (EOM) portion 318, which preferably is used to rapidly squelch the receiver so that 10 the operator does not hear a noise burst.

Referring now to FIG. 4, the preferred embodiment of the encryptor 208 is shown. Preferably, the encryptor 208 operates in the Counter Addressing (CA) mode. As used herein, counter addressing means that the de- 15 vice implementing the selected encryption algorithm is fed a pseudo-random sequence to generate the key stream, which is used to encrypt the plain text message. In this way the encryption device is "addressed" by the pseudo-random sequence. Preferably, the pseudo-ran- 20 dom sequence is provided by a maximal length linear feedback shift register (LFSR). The sequence provided by the LFSR is selected to be such that by knowing a small portion of the sequence, and the rules by which it was created, the entire sequence may be replicated at 25 the receivers. Several such sequences are known in the art and the selection of any particular one is not essential to understanding the present invention.

Referring still to FIG. 4, the pseudo-random sequence is provided by the sequence generator 212 (see 30 FIG. 2) and received by a shift register 400. Preferably, the shift register 400 is 64 bits in length, although other lengths may be used. The shift register 400 parallel loads its entire length as an address to the encryption device 402, which operates to implement any known or 35 proprietary algorithm. The output of the encryption device 402 information is the key stream 404, which is added (modulo two) to the (plain text) signal in the adder 406. The output of the adder 406 is the cipher text stream, which is applied to the compressor 210 (see 40 FIG. 2).

Referring now to FIG. 5, a block diagram illustrating an especially adapted CFB device is shown. A CFB device 500 in the receive mode is chiefly comprised of a shift register 502, an encryption device 504, and a 45 modulo two adder 506. Typically, a differential decoder 512 is employed to avoid having to detect and compensate for phase inversions of the digital stream at the receiver. As is readily apparent, the differentially decoded input signal (CTI) is fed to the encryption algo- 50 rithm 504, which produces a key stream 508. The key stream 508 is added to the differentially decoded input signal (CTI) in the adder 506, which provides the decrypted output signal (PTO). The well known error multiplication problem associated with CFB devices is 55 readily apparent. Assume a single bit is erroneously placed in the shift register 502. This error will be applied the encryption algorithm 504 N times, where N is the length of the shift register. Thus, the error is multiplied by the length of the shift register.

Historically, providers of secure communication equipment developed proprietary encryption algorithms for use with their equipment. This resulted in a proliferation of encryptors each shielded in secrecy to Those of ordinary skill in the art will understand that in both FIGS. 4 and 5, the actual encryption device may be the same, however, their modes of operation are

entirely different. The encryption device is typically realized on a small hybrid device or incorporated into an integrated circuit (IC). Such implementation practice protects the security of the system by making it difficult to analyze the operation of the encryptor. However, the encryptor sealed within the IC or hybrid device is forever constrained to operate only a selected mode. The present invention contemplates that it may be inconvenient to re-design encryptors to operate in the preferred CA mode of operation. Additionally, the present invention seeks to avoid a further proliferation of new encryptors for use in the secure communication system 100 of the present invention. Thus, the present invention contemplates especially adapting CFB devices for use with the present secure communication system.

Still referring to FIG. 5, the LFSR sequence from the sequence generator 212 is operated upon by a differential encoder 510. The purpose of the differential encoder 510 is to counter the effect of the differential decoder 512. The overall result is that differential decoder 512 is effectively removed from the CFB device and reduces the differential encoder and decoder (510 and 512) to mere digital delay elements. Of course, if a particular CFB device 500 did not employ a differential decoder 512, the differential encoder 510 would not be required. This delayed sequence is provided to the shift register 502. The sequence is applied in parallel to the encryption algorithm, which effectively "addresses" the device as seen in FIG. 4. However, the key stream 508 is added to the sequence in the adder 506 and not the plain text message as required. Accordingly, the present invention subtracts out the appropriately delayed (delay 514) sequence (to compensate for the differential decoder and encoder delay) from the key stream in the subtractor 516. Thus, the key stream 508' is added to the plain text signal in the adder 518, which provides the cipher text output to the compressor of FIG. 2. In this way, an existing CFB device 500 operated in the receive mode may be adapted for use in the secure communication system 100 of the present invention.

Referring now to FIG. 6, there is shown the digital compressor 210 of FIG. 2. The compressor 210 is comprised chiefly of an interleave counter 602, a write counter 604, a read counter 606 and a random access memory (RAM) 608. The length of the interleave counter 602 is defined as being the interleave count (N). The write counter 604, the read counter 606 and the RAM 608 are all of a common length referred to as the address count (S), and is equal to the number of data or synchronization bits that will be inserted into the digital information stream. In the preferred embodiment, the interleave count (N) equals 24 and the address count (S) equals 256, although the compressor 210 of the present invention is not constrained to these values and any other values may be selected without departing from the teachings of the present invention. The interleave 60 counter 602, the write counter 604, and the read counter 606 may be any suitable counter and may be implemented in integrated circuit (IC) form or their function may be incorporated as an internal register of a microprocessor or the like. Similarly, the RAM 608 can be maintain the security of the communication system. 65 any suitable memory means having a size (S) that is equal to the amount of data to be inserted and transmitted. As is known, certain microprocessors have an internal RAM area, and provided the RAM is of sufficient

size, all major components of the compressor 210 may reside within a single microprocessor chip.

Operationally, prior to transmission, all counters are preferably reset so that the memory addresses start at zero. The information signal to be transmitted (be it data 5 or digitized voice) is presented to the input port 610 of the RAM 608, and is synchronized to a clock 612. The interleave counter 602 and the write counter 604 begin "up-counting" in synchronization to the clock signal 612. That is, for each clock pulse, the count of the pulses 10 is incremented by a predetermined value (one in the preferred embodiment). The read counter 606 also increments from the clock signal 612. Both the read counter 606 and the write counter 604 reset when they reach the maximum count of S. The write counter 604 15 and the read counter 606 provide the addresses for the RAM 608. As each bit of information is clocked into the RAM 608, a write address is received from the write counter 604 via the switch 620. The switch 620 is controlled by the clock 612, which is also coupled to the 20 RAM's read-write (R/W) control port 609 through the inverter 614. If the memory's R/W signal were inverted, the inverter 614 would not be required. Thus, when the clock signal changes state, the RAM 608 switches to the read mode, and a read address is pro- 25 vided from the read counter via the switch 620.

As previously mentioned, the interleave counter 602 has length N. Accordingly every N clock cycles a pulse will be presented at the interleave counter output 616. This pulse is routed to a reset port 618 of the interleave 30 counter 602, which resets the interleave counter to a logical zero state to resume up-counting again. The output port 616 of the interleave counter 602 also controls the switch 622. When the interleave counter 602 asserts its output pulse, the Nth clock pulse is prevented 35 from reaching the write counter 604 due to the opened switch 622. This keeps the write address the same for two consecutive clocks causing the previous bit to be written over before it is read. The effect is that every Nth bit of the information signal presented at the RAM 40 input port 610 is discarded. For N consecutive clock cycles the read and write addresses are the same. In the compressor, it doesn't matter whether the memory 608 is written to or read from first, however, in the preferred embodiment of the present invention, the mem- 45 ory is first written to. This is done by having counters 602, 604 and 606 increment on the rising edge of the clock and having the switch 620 select the write counter with the memory in the write mode when the clock is a logical one. Other combinations are possible. 50 The first S bits to be read out of the memory 608 are replaced by the synchronization information. The synchronization sequence may be inserted by the switch 214 from the sequence generator 212. Following this, the information signal travels through the RAM 608 on 55 a first-in-first-out (FIFO) basis until all the digital information is sent. In this way the synchronization data may be transmitted after (N-1)XS bits (5,888) bits in the preferred embodiment).

Referring now to FIG. 7, in conjunction with FIG. 6, 60 an illustration of the compressor 210 of FIG. 2 is shown for the simple case of S=9 and N=6. The RAM 608 addresses are arranged from left to right across the top. The clock cycles from the clock 612 are listed sequentially along the left margin. The output 624 of the RAM 65 608 is illustrated down the right hand margin. since S=9, the addressable RAM space is 0-8 inclusive. For illustration purposes, the clock has been selected to start

arbitrarily at zero and may increase without bound. For each clock cycle a read address has been illustrated by "R" and a write address illustrated with the "W". For those cases where the read and write addresses are identical for a given clock cycle, a "WR" is listed in the corresponding column. This notation indicates that the memory 608 is first written to. As previously mentioned, the counters are preferably reset to zero before the process begins. Accordingly, the output of the RAM 608 for bits 0-8 of the RAM 608 are not used so the synchronization signal is transmitted instead. The compressed digital waveform is read out beginning with clock cycle 9. At that time the RAM write address counter 604 has incremented to 8 while the read address counter 606 has been reset back to zero. Therefore, the bit at address zero is read out from the RAM 608 on clock cycle 9 as is indicated in the "output" column. In a similar manner, bit 1 is read out on clock cycle 10, bit 2 on clock cycle 11, and so on. Viewing down the "output" column then it can be seen that bits 5, 11, 17, 23, 29, 35, 41, 47 and 53 have all been deleted from the output stream. The absence of these 9 bits made space for the 9 synchronization bits that were transmitted on clock cycles 0-8. Accordingly, the digital information signal has been compressed to allow the insertion of the synchronization sequence.

Referring now to FIG. 8, the preferred embodiment of the sequence generator 212 of FIG. 2 is shown in block diagram form. The sequence generator 212 provides both the synchronization signal that is interleaved with the encrypted information signal and the pseudorandom "address" signal to the encryption device 208. Preferably, the sequence generator 212 is a maximal length LFSR. Mathematically, the LFSR defines an Nth degree polynomial (where N is the length of the LFSR) with one coefficient for each "tap" or output bit utilized to form the feedback signal. Basically, the preferred sequence generator is comprised of a shift register 800, a plurality of multiplexers 801-806 (or suitable equivalent) and a plurality of modulo two adders 808-812. Each of the multiplexers are coupled to several output bits (taps) of the shift register, one of which is selected via a control bus 816 from the controller 216 of FIG. 2. Initially, the shift register is loaded with an initialization vector in parallel or serially, which comprises a predetermined N-bit digital word. The initialization vector may be pre-stored in the transceiver or may be operator selected such as via the keypad 218. The sequence generator operates to add (modulo two) the selected taps in the adders 808-812. The final adder 812 provides a feedback signal 814, which is also the output of the sequence generator 212. By changing the selected taps via the multiplex control bus 816, different sequences may be generated for use as, for example, different group codes.

To be suitable for use in the present invention, the sequence provided must satisfy three major conditions. First, the polynomial must be irreducible. That is, the polynomial must be divisible only by itself and one. To be irreducible, the number of taps used must be an even integer (6 in the preferred embodiment). Also, irreducibility is required for the LFSR to be maximal length, which is the second condition. Lastly, the polynomial must be self-orthogonal. This is of particular importance if error correction is to be used. A polynomial must have less than 10 taps to be self-orthogonal. In the preferred embodiment of the sequence generator 212, the shift register has a length of 64 bits, thus providing

a 64th degree polynomial. Six taps are used to create the sequence. A 64 bit maximal length LFSR will produce a sequence having 1.84×10<sup>19</sup> bits. At 12 kHz, it would take  $48.7 \times 10^6$  years for the sequence to repeat. Thus, the LFSR of the present invention provides a pseudo- 5 random, noise-like signal suitable for use in a secure communication system.

Referring now to FIG. 9, the synchronization detector 232 of FIG. 2 is shown. The detector 232 is comprised chiefly of a non-inverted detector 900, an in- 10 verted detector 900' and assorted logic which is used to determine whether the inverted or non-inverted detector has found the synchronization sequence. The received data bits enter via the connection 902 and are 904, and is directly supplied to the non-inverted detector 900. The reason for this is that the present invention does not employ differential encoders and must recover the actual logic level. Those of ordinary skill in the art will readily appreciate that phase inversions are a com- 20 mon data transmission problem and that both phases must be investigated to assure synchronization.

Still referring to FIG. 9, the operation of the noninverted detector 900 may be described. The synchronization signal and the data signal are received by a shift 25 register 911. The shift register 911 parallel loads at least a portion of the received data stream to a sequence generator 212'. The sequence generators 212 and 212' are preferably identical since the sequence must be known by both the transmitter and receiver to correctly 30 decode the data on the channel. Additionally, the same taps for the sequence must be selected via the mux control bus 816' if the detector is to locate the synchronization sequence. Those skilled in the art will appreciate that if the synchronization bits that define the logical 35 state of the sequence generator have been properly loaded into the sequence generator 212', both of the sequence generators will be providing the exact same sequence. The locally generated synchronization sequence provided by the generator 212' and the received 40 data stream are compared in an adder 912. Preferably, the adder 912 is a modulo two adder and may be represented as an exclusive OR gate such as an MC14070B manufactured by Motorola, Inc., or its functional equivalent. If the local sequence and the received sequence 45 are identical, the output of the adder 912 will be at a logical "zero" state. Alternately, if the local synchronization sequence and the data stream are dissimilar the output of the adder 912 will be at a logical "one" state. The locally generated sequence and the received se- 50 quence may not be identical for several reasons, including, an error in the received data stream, or that the sequence generator 212' has not been loaded with synchronization bits from the received data stream.

When the output of the adder 912 is at the logical one 55 state, an error has been detected between the received data steam and the locally generated sequence. This output is coupled to an error counter 914, which counts the number of times that the local sequence and the received sequence do not match. Contemporaneously, a 60 second counter 916 is counting clock cycles to form a "window" counter as is known in the art. If the error counter 914 reaches its predetermined count limit, it will generate an output pulse on its output line 918. Output line 918 is operably coupled to the parallel load 65 port 919 of the sequence generator 212' through an AND gate 938. The other input of the AND gate 938 is connected to an inverter 936, which is coupled to the